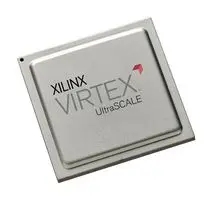

XCVU190-2FLGB2104I 100 % naujas ir originalus nuosavas integrinis grandynas, didelio našumo laikrodžio buferių šeima

Produkto atributai

| TIPAS | APIBŪDINIMAS |

| Kategorija | FPGA (lauko programuojamų vartų masyvas) |

| Mfr | AMD |

| Serija | Virtex® UltraScale™ |

| Paketas | Padėklas |

| Produkto būsena | Aktyvus |

| Programuojamas DigiKey | Nepatikrinta |

| LAB/CLB skaičius | 134280 |

| Loginių elementų/ląstelių skaičius | 2349900 |

| Iš viso RAM bitai | 150937600 |

| I/O skaičius | 702 |

| Įtampa – maitinimas | 0,922 V ~ 0,979 V |

| Montavimo tipas | Paviršinis montavimas |

| Darbinė temperatūra | -40°C ~ 100°C (TJ) |

| Pakuotė / Dėklas | 2104-BBGA, FCBGA |

| Tiekėjo įrenginių paketas | 2104-FCBGA (47,5 x 47,5) |

| Bazinis gaminio numeris | XCVU190 |

apibūdinimas

Kintex® UltraScale FPGA: didelio našumo FPGA, daugiausia dėmesio skiriant kainai ir našumui, naudojant tiek monolitinę, tiek naujos kartos sudėtinio silicio sujungimo (SSI) technologiją.Didelis DSP ir blokinės RAM ir logikos santykis bei naujos kartos siųstuvai-imtuvai kartu su nebrangia pakuote leidžia optimaliai derinti galimybes ir kainą.

Kintex UltraScale+™ FPGA: didesnis našumas ir lustinė UltraRAM atmintis, siekiant sumažinti MK išlaidas.Idealus didelio našumo periferinių įrenginių ir ekonomiško sistemos diegimo derinys.„Kintex UltraScale+ FPGA“ turi daugybę maitinimo parinkčių, kurios užtikrina optimalų balansą tarp reikiamo sistemos našumo ir mažiausio galios.

Virtex® UltraScale FPGA: didelės talpos, didelio našumo FPGA, įgalintos naudojant tiek monolitinę, tiek naujos kartos SSI technologiją.Virtex UltraScale įrenginiai pasiekia didžiausią sistemos pajėgumą, pralaidumą ir našumą, kad patenkintų pagrindinius rinkos ir taikomųjų programų reikalavimus integruodami įvairias sistemos lygio funkcijas.

Virtex UltraScale+ FPGA: didžiausias siųstuvo-imtuvo pralaidumas, didžiausias DSP skaičius ir didžiausia „UltraScale“ architektūroje esanti lustinė ir paketinė atmintis.Virtex UltraScale+ FPGA taip pat siūlo daugybę maitinimo parinkčių, kurios užtikrina optimalų balansą tarp reikiamo sistemos našumo ir mažiausio galios.

Zynq® UltraScale+ MPSoC: Sujunkite ARM® v8 pagrįstą didelio našumo energiją taupantį 64 bitų taikomųjų programų procesorių su ARM Cortex-R5 realaus laiko procesoriumi ir UltraScale architektūra, kad sukurtumėte pirmuosius pasaulyje programuojamus MPSoC.Suteikite precedento neturintį energijos taupymą, nevienalytį apdorojimą ir programuojamą pagreitį.„Zynq® UltraScale+ RFSoC“: sujunkite RF duomenų keitiklio posistemį ir išankstinį klaidų taisymą su pramonėje pirmaujančia programuojama logika ir nevienalyčio apdorojimo galimybėmis. Integruoti RF-ADC, RF-DAC ir minkštųjų sprendimų FEC (SD-FEC) yra pagrindiniai daugiajuosčio ryšio posistemiai. , kelių režimų korinis radijas ir kabelinė infrastruktūra.